성능은 '인텔10나노=삼성·TSMC 7나노'라는 분석도

물리적 측정이 아닌, 성능면에서 '0나노급' 호칭 부여

"메모리는 물리적 측정값과 호칭 비교적 정확히 비례"

삼성, 4세대 D램은 14나노..."업계 최소 수준"

[오피니언뉴스=정세진 기자] 지난주 팻 겔싱어 인텔 최고경영자(CEO)는 2025년까지 1.8나노(nm)급 반도체를 생산하겠다고 발표했습니다.

이날 인텔이 공개한 기술로드맵에 따르면 인텔은 2024년에 2나노급인 20옹스트롬(A) 공정을 구현한 후 1년만에 18A(1A=0.1nm), 즉 1.8나노급 초미세 공정에서 반도체를 양산한다는 계획입니다. 인텔이 계획을 차질없이 진행하면 2025년엔 초미세공정 경쟁력에서 TSMC와 삼성전자를 앞서게 됩니다.

이 계획을 밝히며 인텔은 미세 공정 명칭에 더 이상 나노미터(1㎚는 10억분의 1m)를 붙이지 않기로 했습니다.

펫 겔싱어 CEO는 "인텔의 슈퍼핀은 삼성과 TSMC의 7나노 칩과 비슷한 기술 수준인데 (명칭에 붙는) 숫자가 높아 기술력이 낮다는 오해를 받았다"며 "올 하반기부터 제품 공정에 나노미터 단위를 모두 빼기로 했다"고 말했습니다.

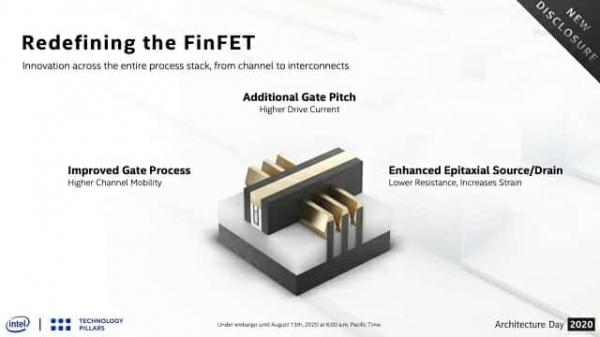

‘0나노급’ 반도체라 부를 때 ‘0나노’는 통상 반도체를 구성하는 트랜지스터 게이트의 물리적 길이를 뜻합니다. 그런데 미세공정 경쟁이 10나노대로 들어서면서 트랜지스터 구조가 2차원 평면이 아닌 3차원으로 진화했습니다. 3차원 ‘핀펫(FinFET)’ 기술 도입 후 트랜지스터 게이트의 물리적 길이는 5나노보다 길지만 성능은 ‘5나노’급이라는 의미에서 ‘5나노 반도체’라고 부릅니다.

미세공정이 발달할수록 반도체 집적도는 높아집니다. 같은 면적에 작은 트랜지스터를 더 촘촘히 박을 수 있는 겁니다. 트랜지스터가 작아지면 동작속도가 빨라져 성능이 개선되고 반도체 원재료인 웨이퍼 한 장에서 더 많은 반도체를 생산할 수 있게 됩니다. 여기에 개별 반도체의 전력 효율도 좋아집니다. 미세공정 경쟁력을 갖추면 더 싼 값에 더 좋은 반도체를 만들 수 있는 겁니다. 삼성전자와 TSMC가 천문학적인 금액을 투자해 미세공정 경쟁에 나서는 이유입니다.

인텔은 현재 반도체 업계에서 통용되는 공정 명칭이 적절치 않다는 입장입니다. 삼성전자와 TSMC가 만든 반도체는 실제 트랜지스터 길이가 7나노가 아니면서 ‘7나노급’ 성능을 가진 반도체에 붙인 이름인데, 성능은 인텔이 ‘10나노’로 이름 붙인 공정에서 만든 제품과 비슷하다는 겁니다.

인텔은 2017년 10나노 공정 도입 계획을 발표하며 자사 반도체는 가로세로 1mm 크기의 면적에 트랜지스터 1억800만개를 심을 수 있지만 삼성전자와 TSMC 제품은 같은 면적에 5000만개를 심는 수준이라고 주장하기도 했습니다.

산제이 나타라잔 인텔 수석 부사장은 “이전 미세공정 이름이 다른 회사와 비교하는데 혼란을 준다는 피드백이 있었다”며 “업계의 일관된 용어를 사용해 고객과 관련 업계 모두가 기술 수준을 쉽게 이해할 수 있도록 미세공정 명칭을 바꿨다”고 설명했습니다.

인텔의 이런 주장은 자사 제품에도 적용되는 이야기일까요. 결론부터 말하면 그렇습니다. 업계에서는 인텔의 로드맵 역시 반도체 성능 측면에서 ‘인텔 20A’는 20옹스트롬 즉, 2나노급 반도체를 의미하고, 18A는 1.8나노급 성능의 반도체를 양산한다는 의미로 해석합니다.

최리노 인하대학교 신소재공학과 교수는 “보통 5나노 반도체라고 할 때 트랜지스터 길이와 공정 명칭에는 괴리가 있다”며 “실제로는 5나노급 성능을 낸다는 의미”라고 말합니다.

최 교수는 “학계에서도 5나노급 반도체 성능이라고 말할 때 기준이 되는 요소에 합의한 건 없다”고 설명합니다.

그렇다면 나노급 반도체의 ‘크기’는 누가, 어떻게 재는 걸까요. 인텔은 내년 7나노 반도체를 선보인 뒤 2023년 3나노, 2024년 2나노, 2025년 1.8나노 반도체를 양산한다는 계획입니다. 일본 니혼게이자이신문, 중국시보 등 외신에 따르면 인텔의 발표 다음날 대만 정부는 TSMC의 2나노 반도체 공장 신설 계획을 승인했습니다. 삼성전자는 내년에 3나노 제품을 양산한다는 계획입니다.

이들 공정에서 생산한 반도체의 ‘키’를 재는 건 팹리스 업계입니다. 인텔은 2나노 공정에서 퀄컴 제품을 생산한다고 밝혔습니다. 퀄컴은 스마트폰에 들어가는 모바일중앙처리장치(AP)를 만드는 회사입니다. 인텔이 만들어 준 반도체를 퀄컴이 다양한 방법으로 정밀하게 테스트해 ‘2나노급’ 성능을 내는지 검증하는 겁니다.

반도체 업계 관계자에 따르면 이런 제품 테스트는 제품을 주문한 퀄컴뿐만 아니라 AP를 만드는 퀄컴 경쟁사와 파운드리 업계의 인텔 경쟁사인 TSMC와 삼성전자도 모두 한다고 합니다. 팹리스와 파운드리 업계에서 경쟁사의 설계나 제조 역량을 확인하는 차원에서 제품의 세부적인 내용까지 꼼꼼히 검증하는 겁니다.

스마트폰이나 노트북 등 일부 제품에 탑재된 반도체는 일반 소비자도 어렵지 않게 성능을 확인할 수 있습니다. 일반적으로 컴퓨터, 스마트폰 등 전자기기의 연산성능을 수치화해 보여주는 ‘벤치마크’ 프로그램을 사용하면 됩니다.

벤치마크 결과는 제품 사용 환경, 소프트웨어와 최적화 정도, 각종 부품을 구성한 하드웨어 제조사 역량 등에 따라 정확도가 다소 떨어질 수 있습니다. 다만 수치화해 보여주기 때문에 AMD는 벤치마크 결과를 인용해 TSMC의 7나노 공정에서 생산한 자사 CPU ‘라이젠5800’의 성능이 인텔 10나노 공정에서 생산한 ‘인텔 코어i7’과 비교해 앞선다고 주장합니다.

그렇다면 메모리 반도체는 어떨까요. 메모리반도체는 시스템 반도체에 비해 상당히 정확한 수치의 선폭을 제품 명칭으로 사용한다고 합니다.

한진만 삼성전자 메모리 담당 부사장은 지난 29일 2분기 실적발표 이후 진행한 컨퍼런스콜에서 "하반기 내놓을 14나노 D램은 14나노대에서 구현 가능한 최소의 선폭"이라며 "EUV를 D램 공정에 선제적으로 적용한 만큼 장기적인 기술리더십 유지의 발판을 확보했다"고 설명했습니다.

메모리 반도체 업계에서는 D램 기술 경쟁이 10나노대에 들어서면서 1x(1세대), 1y(2세대), 1z(3세대), 1a(4세대) 등의 명칭으로 세대를 구분합니다. 10나노급 D램은 같은 세대 제품도 제조사별로 회로선폭이 다릅니다. 삼성전자는 4세대, 즉 ‘1알파’ 세대 제품 중에서는 자사가 최소 선폭(14나노)을 구현했다고 밝힌 겁니다.

삼성전자의 주장이 맞다면 글로벌 시장에서 4세대 D램 점유율이 높아질수록 메모리 반도체 시장에서 삼성의 압도적 영향력은 유지될 가능성이 높습니다.

공정 명칭이 어떻게 바뀌어도 결국 미세공정에서 앞선 제조사가 반도체 시장에서 영향력을 강화한다는 사실에는 변함이 없습니다.

저작권자 © 오피니언뉴스 무단전재 및 재배포 금지